I. Introduction:

In this experiment 5, our group used the QUARTUS II software package to design and simulate a 99 counter. Counters are finite state machines that go from one state to another on each clock pulse. With a general finite state machine the next state that the system goes to depends on the present state and the present inputs. With a counter the next state only depends on the present state. As an example consider a decade down counter. This counter will count through 00 to 99. Each clock pulse forces the counter to the next state or binary output pattern.

II. Objective:

To be able to create a 99 counter with previous symbols.

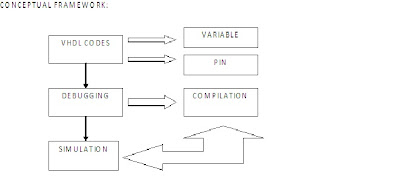

III. Conceptual Framework:

IV. Data and Results:

library ieee;

use ieee.std_logic_1164.all;

entity exp5 is

port(

reset : in BIT;

clk : in BIT;

pause : in BIT;

set : in BIT;

o : OUT BIT;

int : IN INTEGER RANGE 0 TO 9;

r : out bit_vector(3 downto 0);

a : out bit_vector(3 downto 0));

end exp5;

architecture exp5 of exp5 is

BEGIN

PROCESS (clk, reset, pause)

VARIABLE temp : INTEGER RANGE 0 TO 10 := 0;

BEGIN

IF (clk'EVENT AND clk = '1') THEN

if (pause = '0') THEN

temp := temp;

else

temp := temp + 1;

o <= '0';

end if;

IF (temp = 10) THEN

temp := 0;

else

END if;

END if;

END if;

END if;

Results:

|

| DIAGRAM OF EXP 5 |

V. Analysis:

In this experiment, the counter circuit arrives at 99. We analyzed this circuit may on the same wave length certainly. It feed a signal clock at 14 pin cause the position logic at a pin output. From 0 to 99 for switch performs choose RUN or Reset. By seeing the data will understand increasingly.

VI. Conclusion:

Therefore, we concluded that we could derive the equation that describe this counter and implement the 99 counter in dataflow architecture in VHDL. Alternatively, we could describe the structure in terms of AND gates, OR gates, NOT gates and flip-flops. This would be a structural architecture in VHDL.