I. Introduction:

In this experiment 4 our group used the QUARTUS II software package to design and simulate a sequential logic circuit. The requirements for this experiment consists of completing the QUARTUS II designs, printing VHDL source files and simulation results, and completing the laboratory report.

This hardware laboratory exercise is designed to introduce you to a modern computer aided design tool for hardware called Quartus II. The Quartus II software is available on the Windows machines in the laboratory.

Implement the following circuits using VHDL. Provide a timing simulation for the DE2 board. Devise a set of test vectors to verify the circuit. The said experiment gives detailed information on how to create a sequential logic circuit with sequential code.

II. Objective:

To be able to create sequential logic circuit with sequential code.

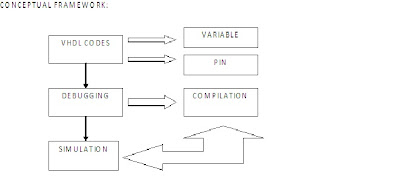

III. Conceptual Framework

IV. DATA and RESULTS:

library ieee;

use ieee.std_logic_1164.all;

entity exp4 is

port(reset : in BIT;clk : in BIT;

pause : in BIT;

set : in BIT;

o : OUT BIT;

int : IN INTEGER RANGE 0 TO 9;

r : out bit_vector(3 downto 0);

a : out bit_vector(3 downto 0));

end exp4;

architecture exp41 of exp4 is

BEGIN

PROCESS (clk, reset, pause;

VARIABLE temp : INTEGER RANGE 0 TO 10 := 0;

BEGIN

IF (clk'EVENT AND clk = '1') THEN

if (pause = '0') THEN

temp := temp;

else

temp := temp + 1;

end if;

IF (temp = 10) THEN

temp := 0;

else

END IF;

END IF;

IF (reset = '0') THEN

temp := 0;

END IF;

CASE temp IS

WHEN 0 => r <= "0000" ;

WHEN 1 => r <= "0001" ;

WHEN 2 => r <= "0010" ;

WHEN 3 => r <= "0011" ;

WHEN 4 => r <= "0100" ;

WHEN 5 => r <= "0101" ;

WHEN 6 => r <= "0110" ;

WHEN 7 => r <= "0111" ;

WHEN 8 => r <= "1000" ;

WHEN 9 => r <= "1001" ;

WHEN OTHERS => null;

END CASE;

CASE int IS

WHEN 0 => a <= "0000" ;

WHEN 1 => a <= "0001" ;

WHEN 2 => a <= "0010" ;

WHEN 3 => a <= "0011" ;

WHEN 4 => a <= "0100" ;

WHEN 5 => a <= "0101" ;

WHEN 6 => a <= "0110" ;

WHEN 7 => a <= "0111" ;

WHEN 8 => a <= "1000" ;

WHEN 9 => a <= "1001" ;

WHEN OTHERS => null;

END CASE;

IF (set = '0') THEN

temp := int;

END IF;

END PROCESS ;

END exp41;

|

| DIAGRAM OF EXPERIMENT 4 |

V. Analysis:

We show in this experiment that multilevel logic synthesis is an effective optimization strategy when targeting designs to lookup table-based FPGAs. Our data gives sequential code for a variable logic function used to illustrate the benefits of multilevel synthesis. In this experiment we will create a new design project which represents the sequential code in our data. Create a sequential design file that comprises the code from our results, as displayed in our data.

VI. Conclusion:

Therefore, we concluded that having implemented the design in the DE2 board, perform a timing simulation to gain a feeling for the timing characteristics of the DE2 board. Once a project has been compiled for the target device, it can be downloaded into a chip by using Quartus II. The procedure for programming a chip is described in our lectures and basically Quartus II is a useful tool for creating sequential logic circuit with sequential codes.

No comments:

Post a Comment